# ICFAITECH NEWSLETTER

**June**

**2025**

## *From the Director's Desk*

It gives me immense pleasure to present this edition of the ICFAI Tech Newsletter, highlighting the vibrant academic, research, and co-curricular activities that continue to shape our institution's excellence.

This quarter has been particularly significant, marked by **remarkable achievements and recognitions**. ICFAI Tech has secured top positions in the Times Engineering Institutes Ranking Survey 2025, including being ranked

**1st among private engineering institutes in Telangana** and **9th overall in India** among 175 leading institutes. These accolades reflect our **collective commitment to academic rigor, industry-relevant research, and holistic student development**.

Our faculty members continue to push the boundaries of knowledge with **high-impact research publications** in reputed journals and conferences. Their contributions not only elevate our academic standing but also bring innovative solutions to real-world challenges.

Events like the **4-week ASIC Design & Implementation Program** in collaboration with MeitY, the **Asana Awakening** yoga session, and our **Environment Day tree plantation drive** showcase our dedication to **skill development, well-being, and sustainability**. These initiatives exemplify how we at ICFAI Tech nurture not just engineers and researchers, but responsible citizens of tomorrow.

I take this opportunity to express my heartfelt appreciation to all faculty members, staff, and students who continue to contribute to the dynamic and inclusive culture of our institution. Let us remain steadfast in our mission to create impactful knowledge, foster innovation, and build a community grounded in excellence and empathy.

**– Dr. K. L. Narayana**

**Director, IcfaiTech,**

**Hyderabad**

## FACULTY ACHIEVEMENTS:

### Research Publications

**Dr. M. Priyadharshini**, Assistant Professor, Dept. of CSE, published a research paper titled "ADHERENT-Net: An Adaptive Health Risk Estimation Network for Real-Time Environmental Tracking," 2025 International Conference on Pervasive Computational Technologies (ICPCT).

**Dr. M. Priyadharshini**, Assistant Professor, Dept. of CSE, published a research paper titled "FedEnv-Net: Federated Neural Network for Decentralized Health Risk Prediction in Dynamic Urban Environments," 2025 International Conference on Pervasive Computational Technologies (ICPCT).

**Dr. M. Priyadharshini**, Assistant Professor, Dept. of CSE, published a research paper titled "A population based optimization of convolutional neural networks for chronic kidney disease prediction" in Scientific Reports.

**Dr. M. Priyadharshini**, Assistant Professor, Dept. of CSE, published a research paper titled "A thermodynamic inspired AI based search algorithm for solving ordinary differential equations" in Scientific Reports.

**Dr. Asisa Kumar Panigrahy**, Associate Professor, Dept. of ECE, published a research paper titled "High-performance AlN/GaN/AlGaN-MOSHEMTs on SiC wafer: scaling and gate material innovations for upcoming radar and communication systems" in the Journal of the Korean Physical Society.

**Dr. Asisa Kumar Panigrahy**, Associate Professor, Dept. of ECE, published a research paper titled "Design and Comparative Analysis of Biosensing Devices with Different Dielectric Materials for Blood Cancer Detection" in SSRG International Journal of Electronics and Communication Engineering.

## FACULTY ACHIEVEMENTS:

### Research Publications

**Dr. Asisa Kumar Panigrahy**, Associate Professor, Dept. of ECE, published a research paper titled “Defect analysis and optimization of nanomaterial-based liner materials for 3D-IC integration” in Analog Integrated Circuits and Signal Processing.

**Dr. Asisa Kumar Panigrahy**, Associate Professor, Dept. of ECE, published a research paper titled “Gate-all-around tree-shaped NSFET-based biosensor: A high-sensitivity approach for label-free biomolecule detection” in Results in Engineering.

### Paper review

**Dr. Asisa Kumar Panigrahy**, Associate Professor, Dept. of ECE, published a research paper titled ‘Cu–Cu Bonding in 3D Integrated Circuits: Thermo-Mechanical Coupling Challenges and Reliability-Driven Solutions’ for International Communications in Heat and Mass Transfer.

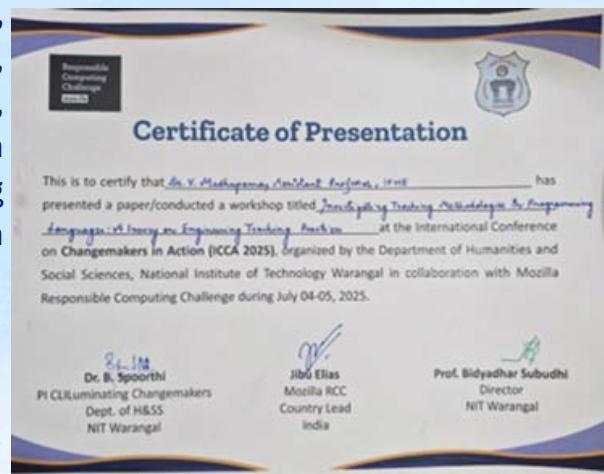

### Paper Presentations

**Dr. V. Madhupama**, Assistant Professor, Department of English, presented a paper on “Investigating Teaching methodologies in programming languages:

A survey on Engineering teaching practices” at the 2-day International Conference “Changemakers in Action” (ICCA-2025), held on July 4–5, 2025, at the Department of Humanities & Social Sciences, NIT Warangal, in collaboration with Mozilla’s Responsible Computing Challenge.

## FACULTY ACHIEVEMENTS:

### Participation

**Dr. Asisa Kumar Panigrahy**, Associate Professor, Dept. of ECE, attended a webinar on has successfully attended webinar on Signal Integrity Analysis Using SIWAVE on 27-05-2025 organised by ARK Info Solution Pvt.Ltd.

**Dr. M. Priyadarshini**, Assistant Professor, Dept. of CSE, has successfully completed the online FDP on Deep Learning organized by SkillDzire in collaboration with AICTE from 17-Mar-2025 to 1-Mar-2025.

## FACULTY ACHIEVEMENTS:

### External Examiner

**Dr. M. Priyadarshini**, Assistant Professor, Dept of CSE, served as the External Examiner for the Ph.D. Defense Viva Voce held on April 11, 2025, at P.K.R. Arts College for Women, affiliated with Bharathiar University, Coimbatore – 641046, Tamil Nadu. The defense was conducted for Mrs. A. Faritha Banu, a Ph.D. candidate from the Department of Computer Science.

### Guest lectures

**Dr. Asisa Kumar Panigrahy**, Associate Professor, Dept. of ECE delivered a guest lecture on " Asic Design and Implementation using Industry Standard EDA Tools, organized by the Centre for VLSI, Department of Electronics and Communication Engineering, IcfaiTech, held from 26th May to 20th June 2025.

**ICFAI** Foundation

for Higher Education

(Deemed-to-be University under Section 3 of the UGC Act, 1956)

Autonomous Institution, Accredited by NAAC with 'A' 3<sup>rd</sup> Grade

**IcfaiTech**

Faculty of Science & Technology (FST)

#### CERTIFICATE OF APPRECIATION

This certificate is proudly presented to

DR. ASISA KUMAR PANIGRAHY ASSOCIATE PROFESSOR, ICFAI TECH (FST), IFHE.

IN GRATEFUL RECOGNITION OF YOUR VALUABLE CONTRIBUTION AS A GUEST SPEAKER FOR

DELIVERING AN INSIGHTFUL LECTURE DURING THE TRAINING AND INTERNSHIP PROGRAM ON **ASIC

DESIGN AND IMPLEMENTATION USING INDUSTRY STANDARD EDA TOOLS**, ORGANIZED BY THE

CENTRE FOR VLSI, DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING, ICFAI TECH,

HELD FROM 26<sup>TH</sup> MAY TO 20<sup>TH</sup> JUNE 2025.

YOUR SESSION SIGNIFICANTLY ENRICHED THE LEARNING EXPERIENCE OF THE PARTICIPANTS AND

ADDED GREAT VALUE TO THE ACADEMIC DISCOURSE.

Program Coordinator

Director-Icfai Tech

## FACULTY ACHIEVEMENTS:

**Asic Design and Implementation using Industry Standard EDA Tools, organized by the Centre for VLSI, Department of Electronics and Communication Engineering, IcfaiTech, held from 26th May to 20th June 2025.**

### 4-Week ASIC Design and Implementation Training using Industry-Standard EDA Tools

#### About the Program

The Centre for VLSI is organizing an intensive 4-week training program on ASIC Design and Implementation using industry-standard EDA tools. This program is intended for B.Tech III and IV year students from all disciplines who are passionate about chip design.

#### Program Highlights

- Introduction to VLSI Chip Design Flow

- Learn Verilog by working on real-world, industry-standard projects

- Hands-on experience with industry-standard EDA tools (Synopsys & Cadence)

- Explore ASIC design flow including logic synthesis, floor planning, and routing

- Gain practical skills in logic synthesis and physical design

- Lectures by internal VLSI experts and industry professionals.

#### Program Details:

Starting from 26<sup>th</sup> May 2025 to 20<sup>th</sup> June 2025

Mode of Study: Offline In-Person

Eligibility : All Engineering Disciplines

**Venue : Centre for VLSI

ICFAI Tech, IFHE Hyderabad**

**EDA tool support provided under the C2S Scheme by ChipIN , MeitY**

**Last Date to Apply**

**12<sup>th</sup> May 2025**

**Registration Link:**

<https://forms.gle/dJ7qbhgmZTEj5syq5>

#### Program Co-ordinators

Dr P Akhendra kumar (Ph:9885708499)

Dr Rajesh Kumar Jha(Ph:9753540139)

Email: [coeinvlsi@ifheindia.org](mailto:coeinvlsi@ifheindia.org)

## ACHIEVEMENTS:

# ICFAI Tech Achieves Top Ranks in Times Engineering Survey 2025

We are proud to share that **ICFAI Tech** has secured outstanding positions in the **Times Engineering Institutes Ranking Survey 2025**, reflecting our unwavering commitment to academic excellence, research, and student success.

## Highlights from the Rankings:

- Ranked 1st among Top 20 Private Engineering Institutes in Telangana

- Ranked 1st in Placement among Top 10 Private Institutes in Telangana

- Ranked 1st in Research Capabilities and Infrastructure among Telangana's Private Institutes

## National Rankings (All India Level):

- 9th Overall among Top 175 Engineering Institutes (Govt. & Private)

- 7th among Top 125 Private Engineering Institutes

- 6th among Top 20 Institutes in the Southern Region

- 7th among Top 70 Private Institutes in Placements

- 10th among Top 30 Institutes in Research Capability (Govt. & Private)

These accolades are a testament to the academic strength, research culture, and industry-aligned focus of ICFAI Tech. We thank all our students, faculty, alumni, and industry partners for being part of this remarkable journey.

## EVENTS

### **Title: 4-Week Job-Oriented ASIC Design and Implementation Program**

**Duration:** May 26 – June 20, 2025

**Organized by:** Dept. of ECE, Faculty of Science and Technology, ICFAI Tech, Hyderabad

**Collaborators:** Ministry of Electronics and Information Technology (MeitY) under the Chips to Startup (C2S) program

**Program Leads:** Dr. P. Akhendra Kumar & Dr. Rajesh Kumar Jha

**Registration Fee:** NIL

**Eligibility:** Final-year UG (all branches) and PG students (ECE) from ICFAI Tech and other institutions

**Participants:** 31 (including external B.Tech and Ph.D. students)

**IcfaiTech**

Faculty of Science & Technology (FST)

### **4-Week ASIC Design and Implementation Training using Industry-Standard EDA Tools**

#### **About the Program**

The Centre for VLSI is organizing an intensive 4-week training program on ASIC Design and Implementation using industry-standard EDA tools. This program is intended for B.Tech III and IV year students from all disciplines who are passionate about chip design.

#### **Program Highlights**

- Introduction to VLSI Chip Design Flow

- Learn Verilog by working on real-world, industry-standard projects

- Hands-on experience with industry-standard EDA tools (Synopsys & Cadence)

- Explore ASIC design flow including logic synthesis, floor planning, and routing

- Gain practical skills in logic synthesis and physical design

- Lectures by internal VLSI experts and industry professionals.

#### **Last Date to Apply**

**12<sup>th</sup> May 2025**

Registration Link:

<https://forms.gle/dJ7qbhgmZTEj5syq5>

#### **Program Co-ordinators**

Dr P Akhendra kumar (Ph:9885708499)

Dr Rajesh Kumar Jha(Ph:9753540139)

Email: [coeinvlsi@ifheindia.org](mailto:coeinvlsi@ifheindia.org)

#### **Program Details:**

Starting from 26<sup>th</sup> May 2025 to 20<sup>th</sup> June 2025

Mode of Study: Offline In-Person

Eligibility : All Engineering Disciplines

**Venue : Centre for VLSI

ICFAI Tech, IFHE Hyderabad**

**EDA tool support provided under the C2S Scheme by ChipIN , MeitY**

## EVENTS

ICFAI Tech successfully organized a **4-Week ASIC Design and Implementation Program** in collaboration with **MeitY** under the **Chips to Startup (C2S)** initiative. Held from **May 26 to June 20, 2025**, the program provided hands-on training using **Synopsys and Cadence EDA tools**, covering the complete ASIC design flow—from **RTL design and simulation to physical design and verification**.

Led by experienced faculty and industry experts, the sessions equipped **31 participants**, including B.Tech and Ph.D. students from various institutions, with practical VLSI skills aligned with current industry demands. The program concluded with expert interactions and career mentoring by professionals from **Pro V Logic** and **Vivek Microchip**.

This initiative reinforces ICFAI Tech's commitment to **skill development and semiconductor research**, fostering industry-ready talent for India's growing VLSI ecosystem.

## EVENTS

### Asana Awakening – Celebrating International Yoga Day at IcfaiTech

On the occasion of **International Yoga Day 2025**, the **Asana Club of IcfaiTech** organized a rejuvenating yoga session titled “**Asana Awakening**” on **20th June 2025 from 10:00 AM to 11:00 AM** at the lush Lawn Area of the campus.

The event aimed to promote physical fitness, mental well-being, and mindfulness among students and staff. Led by renowned yoga trainers **Mr. Sanjay and Ms. Sangeetha**, participants engaged in a dynamic session combining breathing exercises and asanas focused on flexibility, endurance, and inner peace.

Set in a tranquil outdoor setting, the session brought together a vibrant mix of students, faculty, and Asana Club members, reflecting a collective spirit of wellness and harmony. The event concluded with an inspiring address by **Dr. K.L. Narayana, Director of IcfaiTech**, who emphasized the relevance of yoga in managing academic stress and enhancing mental clarity.

“Asana Awakening” was more than just a yoga session—it was a celebration of well-being that left everyone energized, centered, and inspired to make yoga a part of their daily lives.

## EVENTS

### Environment Day Celebration at ICFAI Tech – 5th June 2025

The **Faculty of Science and Technology**, ICFAI Foundation for Higher Education, Hyderabad, celebrated **World Environment Day on 5th June 2025** with great enthusiasm and a strong message of environmental stewardship.

The event was graced by **Prof. K.L. Narayana, Director, ICFAI Tech**, along with **Dr. Anjanna Matta, Associate Dean**, other Associate Deans, and Heads of Departments. To mark the occasion, tree plantation drives were conducted across the campus, symbolizing the commitment of the institution toward building a greener and healthier environment.

**World Environment Day** is a global initiative that calls attention to the urgent environmental challenges we face—including climate change, deforestation, pollution, and biodiversity loss. The event served as a reminder that protecting our planet begins with conscious, everyday actions—from planting trees to adopting sustainable habits.

The collective effort by faculty and staff at ICFAI Tech sent a powerful message: **the Earth is our shared responsibility**, and nurturing it ensures a better future for generations to come.

**ADMISSIONS.ICFAITECH@IFHEINDIA.ORG**

Location: IcfaiTech, IFHE Campus,

Dontanpally, Shankarpally,

R.R Dist, Hyderabad - 501 203

Phone: 040 - 23479725 / 040 - 23479732

Mobile: 8499848444,

Call/Whatsapp: 9010377002

<https://www.ifheindia.org/icfaitech>

<https://www.facebook.com/IcfaiTech/>

<https://in.linkedin.com/company/icfaitech>

## Editorial Team

Dr. K.L. Narayana, Director, IcfaiTech

Dr. Rashmi Sahay, Asst. Prof., CSE, IcfaiTech

Dr. Swathi Mulinti, Asst. Prof., English, IcfaiTech

Dr. Upender Maloth, Asst. Prof., English, IcfaiTech